电源适配器电路设计 |

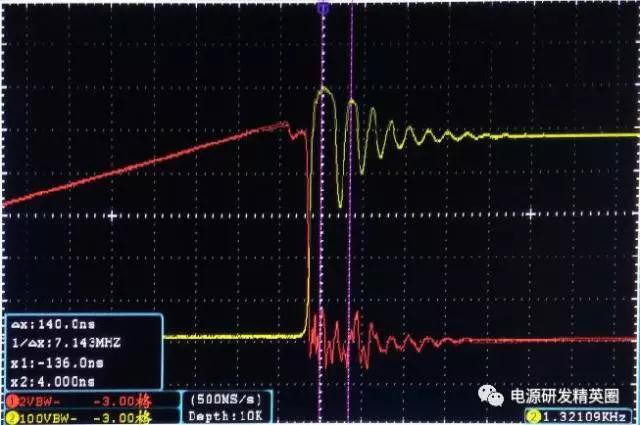

| 1钳位电路 尖峰一定是有的,尖峰大小取决于漏感,钳位功率也取决于漏感。钳位二极管耐压应不低于MOS管耐压,一般应考虑用快恢复的。避免使用4007、磁珠、二极管上串电阻,这些东西是要发热的。钳位电阻应与钳位电容配合,考虑到漏感能量有一部分消耗在开关上,钳位功率控制在漏感的50%以下为宜。  2副边二极管反压尖峰 RC 吸收电路开关电源适配器 非CCM模式,建议在原边MOS驱动上动手脚,增加导通电阻、减缓导通速率、利用米勒效应转移功率、达成减小甚至完全消除副边二极管反压尖峰之目的。此法可完全省掉RC吸收,收获较高整机效率。即使有过渡到CCM模式,上述导通电阻也应做适应性调整,采用一个合理取值,配合RC吸收达成目的。 RC吸收是有损吸收,对于每一个案例、每一个吸收电容值,都有一个较佳电阻值配合使尖峰较小化,找到这个电阻值,达成较小损耗的吸收。在多路输出时,主要的回路才需要RC吸收(并按上面的方法使损耗较小化),次要的回路建议裸奔(用二极管耐压去扛),或者稍微吸收一下即可,切不可喧宾夺主。 3副边二极管耐压 在漏感较小化、吸收较佳配合后,副边二极管电压应力已经较小化了,按此电压应力选择一款较低耐压的肖特基,即达成较高效应用。即使有同步整流助力也应如此。此举是提高整机效率重要的措施之一。 其它电路优化配合 ●副边控制电路耗电较小化设计 尽量在 TL431(1~2mA)范围内解决问题,假负载电流、吸收回路电流亦可利用起来为其供电。避免单独绕组供电的设计。 ●辅助绕组电压较小化设计 以芯片VCC工况为准,电压匹配、电流够用即可,VCC电容容量够用即可。能少一匝就少绕一匝的意思,避免为加快启动而故意增加VCC电流的设计。 ●电流采样电阻Rcs 可能成为PCB板上的热点,也就是损耗点。在必须采样时,应该纠结芯片的采样阀值设置,尽量低一点有利效率;否则可适当减小此电阻值,减小热损失。 ●EMC较优化设计 对高效率电源而言,EMC较优化设计的另一个目的是简化端口的差模共模工程,从而减少器件损耗、提高效率。这些措施是: a、变压器 EMC 结构要追究、隔离屏蔽要做好 b、 PCB 要做好 c、 Y 电容要用两只来湮灭偶极子噪音 d、开关导通速率宜缓不宜急 e、 共模差模结构要合理 ●热平衡设计 仔细考察电源的热景象,主要温升器件的极端较大温升应大致一致,一般可以50C°为限值。温升还可判断变压器设计的合理性、散热工的合理性、意外的温升点意味着高效率设计的败笔。

电路运行层面的设计考虑适配器厂家 文章转载自网络,如有侵权,请联系删除。 |

| | 发布时间:2017.10.27 来源:适配器厂家 |

| 上一个:新时代中国已成电力强国? | 下一个:我国光热发电具备规模化发展条件 |

东莞市玖琪实业有限公司专业生产:电源适配器、充电器、LED驱动电源、车载充电器、开关电源等....